Hello, gentlemen!

I am devouring the masterpiece Understanding the Apple II by Mr. James Sather and the Apple II Reference Manual as well.

So far, so good, but I am stuck on the total amount of RAM available and considered by the system. I am aware that the 6502 processor can read/write 8 bits at a time (8 input/output lines) but has 16 lines available for dealing with addresses.

My issues are:

1) If I have 3 rows of 8 columns with a 16k chip at each socket, how can I have "only" 48k of RAM?;

2) As Apple II Manual Reference states, how can we have 16384 eight-bit bytes of RAM available in a row, if we have eight 16k chips in each row?

Why doesn´t the "summ-them-all" logic apply in this case? I.e., if we have a 64 GB RAM system nowadays, it usually means 2 x 32 GB RAM chips, for example. Apple II has

24 x 16k chips.

Sorry for this noob question but this math is really odd to me...

Thank you for your time.

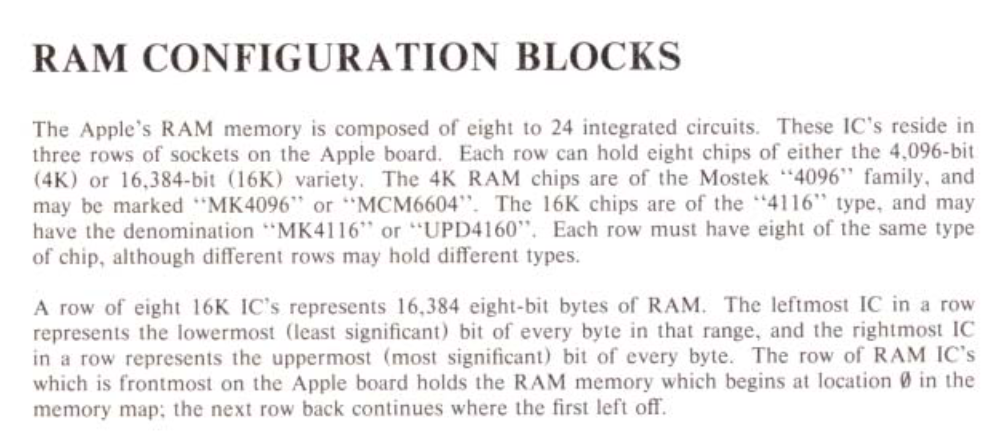

Reread the second paragraph. Each chip has 16 KiloBITS of storage. You need a row of eight to form a byte. One row is a 16 KB block and three of them added together is 48 KB.

The actual datasheets for memory devices (chips, ICs) specify their capacity in bits, because they can be used in systems with any word size. The same chips could be used in rows of 12 to make a PDP-8 clone, for example. At the level of individual chips, bytes are not a concept.

Some later DRAM chips have 4 data bits each, and are combined in sets of 8 to make 32-bit wide, 72-pin SIMMs. (Additional 1 bit-wide chips provide parity bits).

Sorry but I can´t get the relation between 16 kilobits of storage in one chip and 8 chips in a row meaning 16k of storage. Your reply pretty much reaffirms the second paragraph content. That´s exactly the point: I did not get it. Could you please try another approach on the explanation?

Thank you very much for your time.

Each chip is setup so that it handles 1 bit of an 8 bit byte. There are 8 chips on a row to handle each bit of a single byte. Each chip has 16 kilo bits of storage. You need 8 chips for 16 kilo bytes of storage.

For example, if you have a byte that is 10101010. This would be read from right to left with data bit 0 being the right most bit and data bit 7 being the left most bit.

Looking at the board, and using the above byte, the byte is divided up into 8 bits whereby the left-most chip handles bit 0, the second left-most chip handles bit 1, etc.

So, if you would like to write to address BFFF, for example, and put the above byte into that address, the chips on row E would contain that byte. Bit 0, of BFFF would be in chip e3 Bit 1, of BFFF, would be in chip e4. Bit 2, of BFFF, would be in chip e5, etc.

Does that help?

Thank you so much, reifsnyderb! You made everything clearer!

Thank you very much for your time, sir.

One of the benefits of each chip holding 16kb for a single bit of a byte (bit7-bit0) is that when you find an error it's generally rooted in a single bit across all 16k memory locations. This makes fixing easier because you just have the one chip which is home to that single bit to replace. This organization can helpfu in troubleshooting non-working boards, since it's easier to find a cause when there's a single IC responsible for every bit in a 16K range.

If you happen to have an Apple II with the memory blocks on the left side of the motherboard that would be helpful to understand should you find someday you're memory isn't working right. If you wanted to test a single row of 16k (8K or 4K for that matter) you can configure those block to limit the memory available to the system. This can be really helpful, but you'll also need to understand how to wire up your own configuration blocks because those things aren't readily availble today.